Services

Solutions SEEDEA has previously proposed to connect to the next generation

01

High-Speed Communication Interface IP Development

We contribute to the development of our customers' high-speed communication interface through our technological capabilities based on knowledge and experience with state-of-the-art process and high-speed communication technologies.

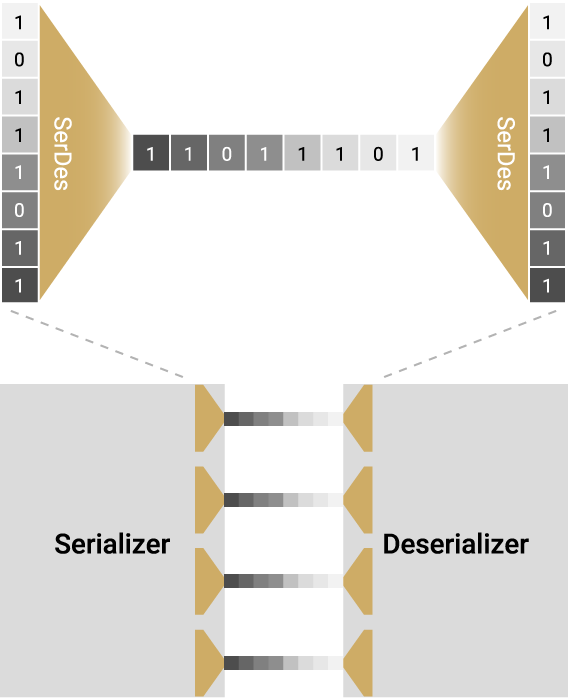

"SerDes" transmits and receives signals at high speed. Serial and parallel interchangeable conversion is performed by combining digital technology and analog technology. The communication speed currently exceeds 10 Gbps.

| Circuit Design | Tx, Rx, etc. |

|---|---|

| Layout Design | Clock Circuit, Power Circuit, Tx, Rx, etc. |

Service Content

High-Speed Interface Macro Development

- 01

- SerDes Macro Shrink Layout

- 02

- SerDes Macro Analog Circuit Design (AMP, DAC VREG, etc.)

- 03

- DDR-PHY Macro Layout Design, Timing Verification (applying purchased macros as hardware macros)

- 04

- High-Speed Interface Circuit Evaluation

Function Overview and Improvements

Problems in high-speed parallel data transmission

- ・

cost increases due to large numbers of I/O pins

- ・

noise influence rises due to an increase in the number of wires on the board

- ・

increase in the degree of difficulty of the timing design

The key to solving these problems is "SerDes technology." We provide support to our customers through advanced technological capabilities.

Achievements

- 01

-

We achieve macro development within target delivery dates and size through analog layout design achievements and technological capabilities based on state-of-the-art processes.

- SerDes Block Layout Shrink: Analog Layout Design and Verification, Floor Plan, Library Environment Improvement

- 02

-

Implementation of macro development with better skills to respond to speed improvement requirements

- Verification of circuit design for high-speed SerDes macro blocks with the speed higher than 10 Gbps, layout design and verification

- 03

-

Creation of hard macros from macros purchased from external sources

- Advanced design technology and P&R technology that does not generate clock skew, timing verification

02

CMOS Image Sensor Development

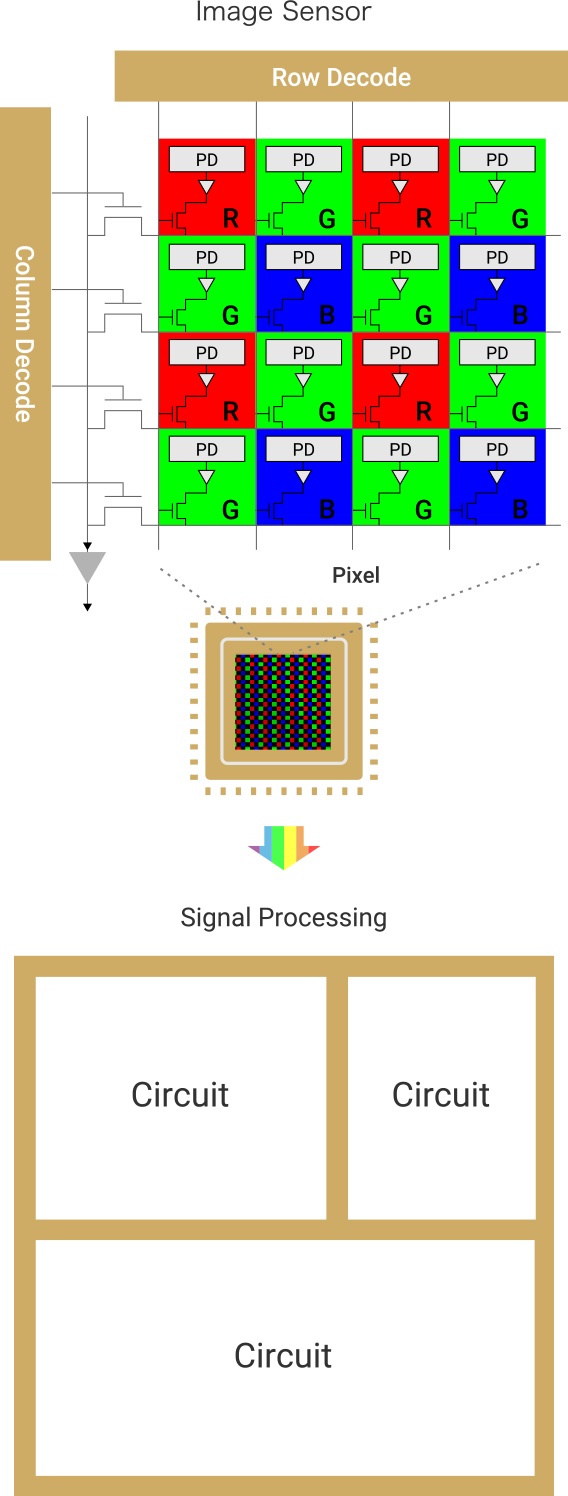

Based on our achievements in the development support offered to semiconductor manufacturers, we provide solid support to our customers' CMOS image sensor development.

The CMOS Image Sensor (CIS) industry is changing rapidly, and because it is driven by the mobile phone market and the automobile market, its market size is expected to reach 16.2 billion dollars by 2020.

Unlike the general digital ASIC and SoC, CIS combines a circuit that processes micro analog signal of image information captured with high sensitivity and ultra-low noise and a transmission circuit that reads digitally processed image information at high speed. This requires a particularly careful response to back-end design.

We have extensive experience helping the development needs of semiconductor manufacturers. This allows us to provide broad support (from back-end design, to circuit design and verification, performance evaluation, etc.) to our customers with their CIS development needs.

Service Content

Development support for smart phone, on-board, and surveillance camera sensors.

- 01

- Middle and Back-End Design Logic Synthesis, DFT, P&R, STA, Layout Design and Verification, TOP Layout

- 02

- Circuit Design and Verification, Analog Part Layout Design (MIPI, etc.) and Verification, Digital Part Logic Design and Verification

Function Overview and Improvements

More advanced LSI design technologies, such as CIS high pixelization, high quality image, and high reliability requirements are essential. As our engineers, who possess solid technological capabilities acquired from our experience, we apply new design technologies based on the know-how cultivated while accumulating an incredible CIS development track record, and continue to contribute to the development of CIS as a strategic partner.

Achievements

- 01

-

Development of new component technologies and examination of new process technologies

- Highly novel digital circuit back-end design (from feasibility study to product tape out), and feasibility study of newly developed processes

- Establishment and lateral growth (joint development with regard to design technology) of a Multi-Power Supply design flow for the realization of ultra-low power CIS

- 02

- Advanced Analog Circuit, Layout Design (AMP, ADC, VREG, VREF, High-Speed I/F)

- 03

- Logic design of high-speed processing control units for large-scale image data and efficient verification of image data based on high pixelization

- 04

- Quality Improvement, Man-hour Reduction

(From an overall back-end design viewpoint, improvement of QoR as well as reduction of man-hour through the development, management, and deployment of a common automation environment)

03

Public Transportation System Development

We contribute to the smart development of social systems with embedded development capabilities for major electric manufacturers.

In the ever-evolving social systems, the railway transportation system will continue to develop as a solid infrastructure.

Systems that support railway transportation, such as operation control, automatic train control, train security, and vehicle information, consist of large-scale embedded systems.

Service Content

- 01

-

Software development

- Development of embedded, control, and UI software

- Management of software update points

- Creation and management of revision plans (PAD chart)

- 02

-

System development

- Control process, recording process (fault and operation status recordings), and board development

- 03

-

System operation

- Unit, combination, and system tests

Function Overview and Improvements

In highly public systems, steady operation as well as high and flawless reliability are required. In order to respond to this, we maintain process continuity and reliability based on the "2 out of 3" method according to the manufacturer and the three types of systems.

Achievements

- Automatic Train Control Device (ATC/S) Development

- 01

- Smooth system startup support with the implementation of special processes that prevent unnecessary system error outputs

- 02

- More compact package design achieved through the standardization of embedded software functions

- 03

- In the event of a fault, real-time automatic recording of information to internal memory card to contribute to early detection of the location and repair of a particular error

- 04

- Automatic recording to memory card of all internal information until correct and complete system shutdown, and total support of operation control